## 2023 IEEE ASSCC Review

서울대학교 전기정보공학부 박사과정 박현준

## Session 10 Computing and Analog Circuit for Next Generation Memories

Session 10은 고속 데이터 전송 및 메모리 인터페이스의 최신 동향과 혁신적인 해결책들을 제시한다. 고대역폭 메모리 인터페이스, 효율적인 신호 전송 기술에 관한 5개의 중요한 논문이 발표되었다. 이들 논문은 기존의 데이터 전송 방식을 넘어서는 혁신적인 접근방식을 제시하며, 특히 메모리 인터페이스 및 통신 시스템의 성능과 효율성을 대폭 향상시키는 데 중요한 기여를 하였다. 51.2T 이더넷 스위치를 위한 실리콘 광학 트랜시버부터고대역폭 메모리 접근을 위한 PAM-4 드라이버, 고밀도 I/O 통신을 위한 인코더 기반 crosstalk 제거 트랜시버, 시간 기반 PAM-4 트랜시버, 그리고 고성능 PLL 주파수 합성기에 이르기까지, 다양한 논문들이 소개되었다.

#10-1 이 논문은 51.2T 이더넷 스위치에 대한 새로운 요구 사항을 충족하기 위해, 대역 폭을 증가시키기 위한 실리콘 광학 기반의 트랜시버 Front-End를 소개한다. 기존의 플러그 가능한 광학 모듈과 달리, 이 연구에서 제안된 통합된 공동 포장 광학(Co-Packaged Optics, CPO)은 디지털 신호 처리기(DSP) 대신 선형 드라이버와 CTLE를 사용하여 전력소비를 크게 줄입니다. 또한, 맞춤형 실리콘 광학 모듈레이터와 포토디텍터를 사용하여, 기존 시스템보다 더 나은 성능과 배열 통합을 달성한다. 이 시스템은 112 Gb/s의 데이터전송 속도를 달성하며, 이는 기존의 솔루션들과 비교하여 상당한 개선을 나타낸다. 특히, 이 기술은 기존의 광학 모듈 대비 훨씬 낮은 전력 소비를 가능하게 하며, 데이터 센터의대역폭 밀도를 향상시킨다.

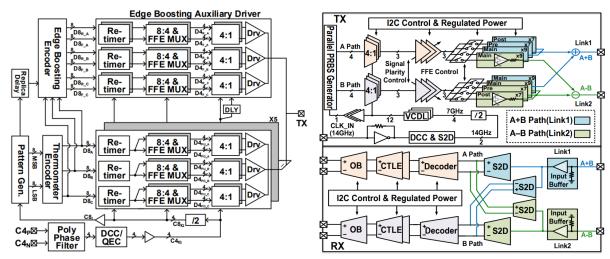

[그림 2] (좌) 10-2 (우) 10-3

#10-2 이 논문은 고대역폭 메모리 접근의 요구 증가에 대응하기 위해, 28-nm CMOS 기술로 구현된 80Gb/s PAM-4 Single-Ended 전압 모드 드라이버를 제시한다. 이 전송기는 채널 equalizing을 위해 4-탭 FFE와 에지 부스팅 보조 드라이버를 포함한다. 이 시스템은 80Gb/s의 데이터 전송 속도를 달성하며, 297mV의 전압 스윙과 최악의 경우 약 45mV의 아이 오프닝을 제공한다. FFE를 사용하여 채널 손실에 대한 등화를 달성함으로써, 전체파워 소비는 246mW로, 80Gb/s에서 3.07pJ/bit의 에너지 효율을 보여준다.

#10-3 이 논문은 28nm CMOS 기술로 제작된, 인코더 기반의 crosstalk 제거 기능을 갖춘 2×24Gb/s Single-Ended 트랜시버를 제시한다. 이 디자인은 특히 고밀도 I/O 통신을위한 새로운 방법을 제공하며, 채널간 crosstalk을 효과적으로 제거합니다. 구체적으로, 인코더 기반 교차 간섭 제거 (EB-XTC) 방식으로 신호를 두 개의 직교하는 구성요소로 분해하여, 채널 의존성 없이 교차 간섭을 억제한다. 즉, 다양한 채널의 물리적 특성에 민감하지 않으며, 여러 채널 시나리오로 확장 가능하다. 이 트랜시버는 2개의 wire channel을 사용하는데, CH1에서 -2dB에서 -65dB로, CH2에서 -10dB에서 -26dB로 교차 간섭을 감소시켰다. 또한, 이 시스템은 불균형한 채널에서도 차동 전송과 유사한 성능을 달성하며, 시스템의 등화 요구 사항을 크게 완화시킨다. 전체 TRX는 레인 당 0.03mm²의 면적을 차지하며, 레인 당 69.5mW의 전력을 소비하며, 2.9pJ/b의 전력 효율을 제공한다.

#10-4 이 논문은 메모리 인터페이스를 위한 고속 트랜시버의 수요 증가에 대응하여, 단일 경로 디코딩 스킴과 빠른 확률적 교정 기술을 사용하는 시간 기반 PAM-4 트랜시버를 제안한다. 이 트랜시버는 전력 효율성을 높이고 신호 무결성을 개선하기 위해 여러가지 아이디어를 제안하였다. PAM-4 신호의 MSB와 LSB를 복구하기 위해 단일 경로를 사용하여 기존 방식 대비 지연 로직 및 비교기의 수를 크게 줄이고, 전압과의 선형 관계를 갖

는 선형 VTC를 사용하여 레벨 불일치 비율(RLM)을 향상시킵니다. 또한, 확률적 교정 으로 VTC 이득, 단일-차동 증폭기(S2D), 시간 임계값(TTH), 결정 피드백 이퀄라이저(DFE)의 robustness를 향상시킨다. 기존의 시간 기반 PAM-4 디코딩 방식과 비교하여 구성 요소를 크게 줄여 전력 효율을 높였고 VTC는 RLM 0.96을 달성하여 기존 VTC(RLM 0.18) 대비향상된 성능을 보여준다. Calibration scheme은 PVT 변동에 강한 내성을 가지며, 교정 절차를 단순화하여 신호 무결성을 개선한다.

#10-5 이 논문은 mm-파 고속 무선 통신 시스템 및 데이터 변환기에 필수적인 낮은 지터를 가진 PLL 주파수 합성기를 제시한다. 65nm CMOS 공정으로 제작된 쿼드 코어 VCO를 사용하여 11.6-to-13.6GHz 범위에서 47-fsrms 지터와 1MHz 오프셋에서 -128dBc/Hz의 위상 잡음을 달성한 Integer-N PLL을 소개한다. 기본 주파수 성분을 억제하면서 Second 하모닉 출력을 위한 고품질의 로컬 발진기 신호를 생성한다. 공통 모드 공진을 사용하여 낮은 위상 잡음을 달성하며, 저항 동기화된 쿼드 코어 VCO는 효과적인 동기화효과와 낮은 위상 잡음에 기여한다. 빠른 스토캐스틱 교정 기술은 VCO의 위상 잡음을 줄이고 PLL의 대역폭을 최적화하여 밴드 내 잡음을 억제한다. 이를 바탕으로 제안된 PLL은 11.6-to-13.6GHz 범위에서 47-fsrms 지터를 달성하며, 측정된 위상 잡음은 1MHz 오프셋에서 -123.25dBc/Hz로, second 하모닉 출력에서는 -111.57dBc/Hz이다. 이 PLL은 mm-파 고속 무선 통신 시스템 및 데이터 변환기에 매우 적합한 낮은 지터와 고성능 위상 잡음 특성을 제공한다.

## 저자정보

## 박현준 박사과정 대학원생

● 소속 : 서울대학교

● 연구분야: HBM, Chord Signaling, Information Theory

• 이메일 : spp098@snu.ac.kr

• 홈페이지: https://sites.google.com/view/wschoi?pli=1